## KONGUNADU COLLEGE OF ENGINEERING AND TECHNOLOGY (AUTONOMOUS)

# DEPATMENT OF COMPUTER SCIENCE AND ENGINEERING

SUBJECT CODE:24EC304

SUBJECT NAME: DIGITAL LOGIC AND COMPUTER ORGANIZATION

## UNIT-I DIGITAL FUNDAMENTALS

Number Systems – Decimal, Binary, Octal, Hexadecimal, radix conversion ,1's and 2's complements, Codes – Binary, BCD, Excess 3, Gray, Alphanumeric codes, Boolean theorems & Postulates, Logic gates, Universal gates, Sum of products and product of sums, Minterms and Maxterms, Karnaugh map Minimization

#### UNIT-I BOOLEAN ALGEBRA AND LOGIC GATES

#### Number Systems:

Number system is a basis for counting various items

The decimal number system has 10 digits:0,1,2,3,4,5,6,7,8 and 9

Types of Number Systems:

| System       | Base | Symbols       |  |  |  |

|--------------|------|---------------|--|--|--|

| Decimal      | 10   | 0,1,2,9       |  |  |  |

| Binary       | 2    | 0,1           |  |  |  |

| Octal        | 8    | 0,1,2,7       |  |  |  |

| Hexa-decimal | 16   | 0,1,2,9,A,B,F |  |  |  |

| Decimal | Hexadecimal | Binary (421/8421) |

|---------|-------------|-------------------|

| 0       | 0           | (0)000            |

| 1       | 1           | (0)001            |

| 2       | 2           | (0)010            |

| 3       | 3           | (0)011            |

| 4       | 4           | (0)100            |

| 5       | 5           | (0)101            |

| 6       | 6           | (0)110            |

| 7       | 7           | (0)111            |

| 8       | 8           | 1000              |

| 9       | 9           | 1001              |

| 10      | A           | 1010              |

| 11      | В           | 1011              |

| 12      | C           | 1100              |

| 13      | D           | 1101              |

| 14      | Е           | 1110              |

| 15      | F           | 1111              |

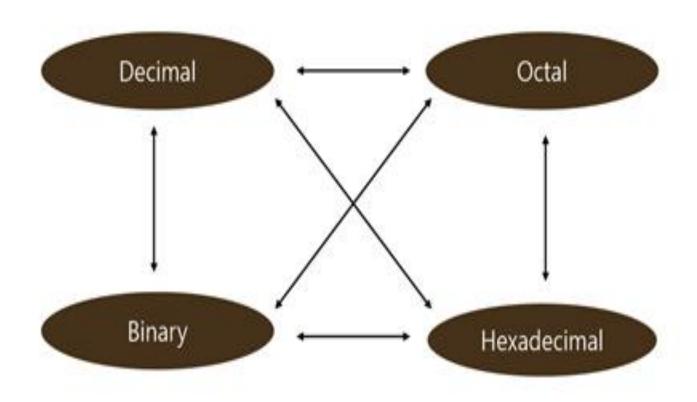

### **Conversion among Bases**

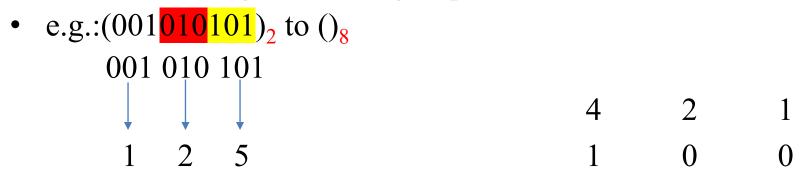

#### Binary to Octal

- Group into 3's starting at least significant bit (if the number of bits is not evenly divisible by 3, then add 0's at the most significant end)

- write 1 octal digit for each group

Answer =  $125_8$

#### Octal to Binary

• For each of the Octal digit write its binary equivalent e.g.: (257)<sub>8</sub> to ()<sub>2</sub>

Answer =  $(010101111)_2$

e.g.:  $(125.62)_8$  to  $()_2$

$\longrightarrow$  (1010101.11001)<sub>2</sub>

## Binary to Hexadecimal

- Group into 4's starting at least significant bit (if the number of bits is not evenly divisible by 4, then add 0's at the most significant end)

- write 1 hex digit for each group.

Answer =

$$(2BB)_{16}$$

e.g.:  $(001101101101.10011010)_2$  to  $()_{16}$

$(00)11 \ 0110 \ 1110 \ . \ 1001 \ 101(0)$

$3 \ 6 \ E \ . \ 9 \ A \longrightarrow (36E.9A)_{16}$

## Hexadecimal to Binary

- For each of the Hex digit write its binary equivalent(use 4 digits to represent)

- e.g.:  $(8A9.B4)_{16}$  to  $()_2$

8 A 9 . B 4

1000 1010 1001 . 1011 01<mark>00</mark>

$\longrightarrow$  (100010101001.101101)<sub>2</sub>

#### Octal to Hexadecimal

#### Steps:

- 1.Convert octal number to its binary equivalent

- 2.Convert binary number to its hexadecimal equivalent

e.g.:

$$(615.25)_8$$

to  $()_{16}$

| 6      | 1    | 5    | • | 2    | 5      | ן |        |

|--------|------|------|---|------|--------|---|--------|

| 110    | 001  | 101  | • | 010  | 101    |   | Step 1 |

|        | 1    | L    |   |      |        |   |        |

| (000)1 | 1000 | 1101 |   | 0101 | 01(00) |   | Step 2 |

| 1      | 8    | D    |   | 5    | 4      |   |        |

$$(615.25)_8 \longrightarrow (110001101.010101)_2 \longrightarrow (18D.54)_{16}$$

#### Hexadecimal to Octal

#### Steps:

- 1. Convert hexadecimal number to its binary equivalent

- 2. Convert binary number to its octal equivalent

e.g.: (BC66.AF)<sub>16</sub>to ()<sub>8</sub>

| В                                |     | $\mathbb{C}$ | 6    |     | 6   | • | A   |     | F    |        |

|----------------------------------|-----|--------------|------|-----|-----|---|-----|-----|------|--------|

| 1011                             | 11  | 00           | 0110 | 01  | 10  | • | 101 | 0   | 1111 | Step 1 |

| (00)1011110001100110.10101111(0) |     |              |      |     |     |   |     |     |      |        |

| 001                              | 011 | 110          | 001  | 100 | 110 |   | 101 | 011 | 110  | Step 2 |

| 1                                | 3   | 6            | 1    | 4   | 6   |   | 5   | 3   | 6    |        |

$$(BC66.AF)_{16} \longrightarrow (1011110001100110)_2 \longrightarrow (136146.536)_8$$

#### Converting any radix to decimal

- Converting from any base to decimal is done by multiplying each digit by its weight and summing.

- Ex: Convert (3102.12)<sub>4</sub> to its decimal equivalent

$$N=3*\frac{4^{3}}{4^{3}}+1*\frac{4^{2}}{4^{2}}+0*\frac{4^{1}}{4^{1}}+2*\frac{4^{0}}{4^{0}}+1*\frac{4^{-1}}{4^{-1}}+2*\frac{4^{-2}}{4^{-2}}$$

$$=192+16+0+2+0.25+0.125=(210.375)_{10}$$

• Ex: Determine the value of base x, if  $(193)_{x} = (623)_{8}$

Converting octal into decimal:

$$(623)_8 = 6*8^2 + 2*8^1 + 3*8^0 = (403)_{10}$$

$(193)_x = 1*x^2 + 9*x^1 + 3*x^0 = (403)_{10}$

$x^2 + 9x + 3 = 403$   $\longrightarrow$   $x = 16 \text{ or } -25$

Negative not applicable so  $(193)_{6}$ = $(623)_{8}$

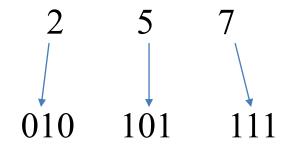

#### Conversion of Decimal number to any Radix number

#### Steps:

- 1. Convert integer part (Successive Division Method)

- 2. Convert fractional part (Successive Multiplication Method)

- Steps in Successive Division Method:

- Divide the integer part of decimal number by desired base number, store quotient (Q) and remainder (R)

- Consider quotient as a new decimal number and repeat step1 until quotient becomes 0

- List the remainders in the reverse order

- Steps in Successive Multiplication Method:

- ➤ Multiply the fractional part of decimal number by desired base number

- ➤ Record the integer part of product as carry and fractional part as new fractional part

- ➤ Repeat steps 1 and 2 until fractional part of product becomes 0 or until you have many digits as necessary for your application

- > Read carries downwards to get desired base number

- Convert 12.125 decimal to binary

- Integer Part:

Fractional Part:

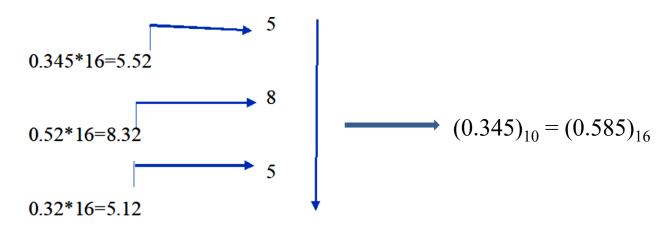

- Convert 5386.345 decimal to hexadecimal

- Integer Part:

#### Fractional Part:

$(5386.345)_{10} = (150A.585)_{16}$

#### 1's Complement

The 1's complement of a binary number is the number that results when we change all 1's to zeros and the zeros to ones.

| 1           | 1             | 0 | 1 | 0 | 1 | 0 | 0 |  |  |  |

|-------------|---------------|---|---|---|---|---|---|--|--|--|

|             | NOT operation |   |   |   |   |   |   |  |  |  |

| 0 0 1 0 1 1 |               |   |   |   |   |   |   |  |  |  |

Number

1's Complement

2's Complement

The 2's complement the binary number that results when add 1 to the 1's complement.

2's complement = 1's complement + 1

| 1             | <mark>1</mark> | 0              | 0 | 0 | <mark>1</mark> | 0 | 0 |  |  |  |  |

|---------------|----------------|----------------|---|---|----------------|---|---|--|--|--|--|

| NOT operation |                |                |   |   |                |   |   |  |  |  |  |

|               |                |                |   |   | 1              | 1 |   |  |  |  |  |

| 0             | 0              | 1              | 1 | 1 | 0              | 1 | 1 |  |  |  |  |

|               |                |                |   |   |                |   | 1 |  |  |  |  |

| 0             | 0              | <mark>1</mark> | 1 | 1 | <mark>1</mark> | 0 | 0 |  |  |  |  |

Number

Carry

1's Complement

Add 1

2's Complement

• 9's Complement

The nines' complement of a decimal digit is the number that must be added to it to produce 9. The complement of 3 is 6, the complement of 7 is 2.

• Example: Obtain 9's complement of 7493

9999

-7493

------

2506

$$\rightarrow$$

9's complement

10's Complement

The 10's complement of the given number is obtained by adding 1 to the 9's complement.

10's complement = 9's complement + 1

Example: Obtain 10's complement of 7493

10's complement

## **Arithmetic Operations**

#### Binary Addition

The addition consists of four possible elementary operations:

| S.No | Operations             |

|------|------------------------|

| 1    | 0+0=0                  |

| 2    | 0+1=1                  |

| 3    | 1+0=1                  |

| 4    | 1+1=10(0 with carry 1) |

In the last case, sum is of two digits: Higher Significant bit is called Carry and lower significant bit is called Sum.

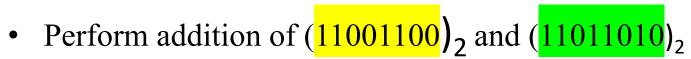

| 1   | 1 |   | 1 | 1 |   |   |   |   | Carr  |

|-----|---|---|---|---|---|---|---|---|-------|

|     | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | Numbe |

| (+) | 1 | 1 | 0 | 1 | 1 | 0 | 1 | 0 | Numbe |

| 1   | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | Resu  |

**'**y

er 1

er 2

ılt

• Add  $(28)_{10}$  and  $(15)_{10}$  by converting them to binary

| 1   | 1 | 1 |   |   |   | Carry       |

|-----|---|---|---|---|---|-------------|

|     | 1 | 1 | 1 | 0 | 0 | $(28)_{10}$ |

| (+) | 0 | 1 | 1 | 1 | 1 | $(15)_{10}$ |

| 1   | 0 | 1 | 0 | 1 | 1 | $(43)_{10}$ |

#### Binary Subtraction

• The subtraction consists of four possible elementary operations:

| S.No | Operations       |                                               |

|------|------------------|-----------------------------------------------|

| 1    | 0-0=0            | In case of second operation                   |

| 2    | 0-1=1 (borrow 1) | the minuend bit is smaller                    |

| 3    | 1-0=1            | than the subtrahend bit, hence 1 is borrowed. |

| 4    | 1-1=0            | nence i is bollowed.                          |

Perform (11101100)<sub>2</sub> -(00110010)<sub>2</sub>

|     |   |          | (10) 0   | 10             |                | 0         | 10             |                |          |

|-----|---|----------|----------|----------------|----------------|-----------|----------------|----------------|----------|

|     | 1 | <u>1</u> | <u>1</u> | <mark>Ø</mark> | 1              | <u> 1</u> | <mark>Ø</mark> | <mark>0</mark> | Number 1 |

| (-) | 0 | 0        | 1        | 1              | <mark>0</mark> | 0         | 1              | 0              | Number 2 |

|     | 1 | 0        | 1        | 1              | 1              | 0         | 1              | 0              | Result   |

#### **Binary Subtraction using 1's complement**

• Perform subtraction using 1's complement  $(11010)_2$  -  $(10000)_2$

Step 1: 1's complement negative number

$$(10000)_2 \longrightarrow (01111)_2$$

Step 2: Add  $(11010)_2$  and  $(011111)_2$

| 1 | 1 | 1 | 1 |   |                  |                |

|---|---|---|---|---|------------------|----------------|

|   | 1 | 1 | 0 | 1 | 0                |                |

|   | 0 | 1 | 1 | 1 | 1                |                |

|   |   |   |   |   |                  |                |

| 1 | 0 | 1 | 0 | 0 | 1                |                |

|   |   |   |   |   | <mark>→ 1</mark> | Add end-around |

|   | 0 | 1 | 0 | 1 | 0                | carry          |

Note: If carry is generated then the result is positive and in the true form so aa carry to the result to get final result

• Perform subtraction using 1's complement  $(15)_{10}$  - $(28)_{10}$

Binary equivalent:  $(1111)_2$  -  $(11100)_2$

Step 1: 1's complement negative number

$$(\boxed{11100})_2 \qquad \longrightarrow \qquad (\boxed{00011})_2$$

Step 2: Add  $(1111)_2$  and  $(00011)_2$

|     | 1                                                                                                  | 1 | 1              | 1              |   |                                                                   |  |  |  |  |  |  |

|-----|----------------------------------------------------------------------------------------------------|---|----------------|----------------|---|-------------------------------------------------------------------|--|--|--|--|--|--|

|     | 0                                                                                                  | 1 | <mark>1</mark> | <mark>1</mark> | 1 | $(15)_{10}$                                                       |  |  |  |  |  |  |

| (+) | 0                                                                                                  | 0 | 0              | 1              | 1 | 1,s complement of $(28)_{10}$                                     |  |  |  |  |  |  |

|     | 1                                                                                                  | 0 | 0              | 1              | 0 | Result                                                            |  |  |  |  |  |  |

|     | In this case the carry is not generated then the result is negative and in the 1's complement form |   |                |                |   |                                                                   |  |  |  |  |  |  |

|     | 0                                                                                                  | 1 | 1              | 0              | 1 | Verification (1's complement form of result) $\frac{(13)_{10}}{}$ |  |  |  |  |  |  |

#### Binary Subtraction using 2's complement

- Perform subtraction using 2's complement binary arithmetic  $(147)_{10}$   $-(89)_{10}$

- Step 1: Binary equivalent  $(010010011)_2$  - $(01011001)_2$

- Step 2: Find 2's complement of (89)<sub>10</sub>

| 1 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 1's complement of (89) <sub>10</sub> |

|---|---|---|---|---|---|---|---|--------------------------------------|

|   |   |   |   |   |   |   | 1 | Add 1                                |

|   |   | 1 |   |   | 4 | 1 | 1 | 2's complement of $(89)_{10}$        |

| 1   | 1 |   |   |   |   | 1 | 1 | 1 |   |                                   |

|-----|---|---|---|---|---|---|---|---|---|-----------------------------------|

|     | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | Binary equivalent of $(147)_{10}$ |

| (+) | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 2's complement of $(89)_{10}$     |

| 1   | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 0 | Result                            |

Note: If carry is generated then the result is positive and in the true form so the carry is ignored.

#### **Binary Subtraction using 2's complement**

• Perform subtraction using 2's complement  $(42)_{10}$  - $(68)_{10}$

• Step 1: Binary equivalent  $(101010)_2$  - $(1000100)_2$

• Step 2: Find 2's complement of  $(68)_{10}$

| 1 | 0 | 0 | 0 | 1 | 0 | 0 | Binary equivalent of (68) <sub>10</sub> |

|---|---|---|---|---|---|---|-----------------------------------------|

| 0 | 1 | 1 | 1 | 0 | 1 | 1 | 1's complement of (68) <sub>10</sub>    |

|   |   |   |   |   |   | 1 | Add 1                                   |

| 0 | 1 | 1 | 1 | 1 | 0 | 0 | 2's complement of (68) <sub>10</sub>    |

|     |   | 1 | 1 |   |   |   |   |                                      |

|-----|---|---|---|---|---|---|---|--------------------------------------|

|     | 0 | 1 | 0 | 1 | 0 | 1 | 0 | Binary equivalent of $(42)_{10}$     |

| (+) | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 2's complement of (68) <sub>10</sub> |

|     | 1 | 1 | 0 | 0 | 1 | 1 | 0 | Result                               |

Note: If carry is not generated then the result is negative and in the 2's complement form

| 1 | 1 | 0 | 0 | 1 | 1 | 0 | Result                            |  |

|---|---|---|---|---|---|---|-----------------------------------|--|

| 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1's complement                    |  |

|   |   |   |   |   |   | 1 | 2's complement                    |  |

| 0 | 0 | 1 | 1 | 0 | 1 | 0 | ( <mark>26</mark> ) <sub>10</sub> |  |

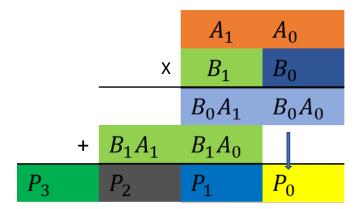

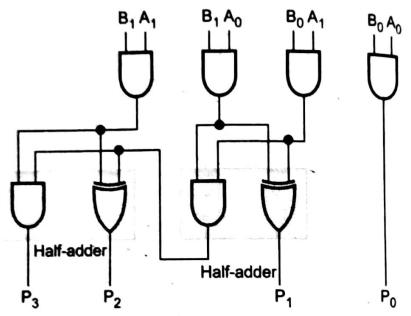

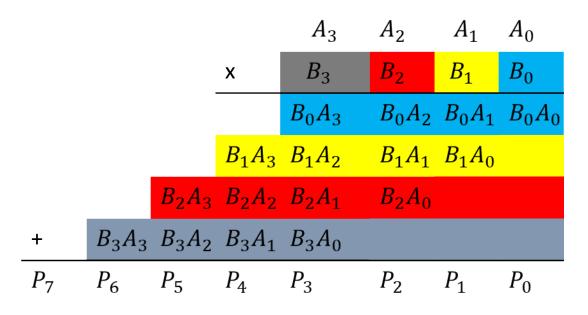

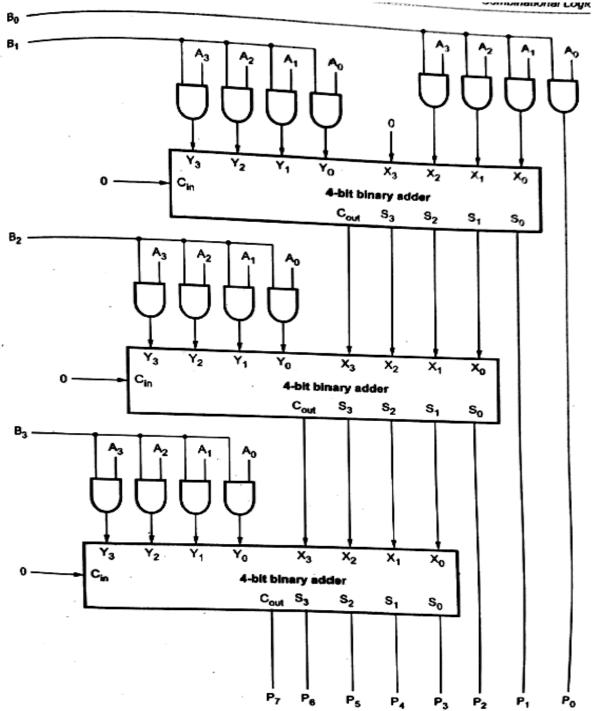

#### **Binary Multiplication**

Rules for Binary Multiplication are:

| S.No | Operations |

|------|------------|

| 1    | 0*0=0      |

| 2    | 0*1=0      |

| 3    | 1*0=0      |

| 4    | 1*1=1      |

Multiply (101.11)<sub>2</sub> and (110.01)<sub>2</sub> using binary multiplication method

|   |   |   |   | 1 | 0 | 1 |   | 1 | 1 | Multiplicand |

|---|---|---|---|---|---|---|---|---|---|--------------|

|   |   |   | X | 1 | 1 | 0 | • | 0 | 1 | Multiplier   |

|   |   |   |   |   | 1 | 0 | 1 | 1 | 1 |              |

|   |   |   |   | 0 | 0 | 0 | 0 | 0 | 0 |              |

|   |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 |              |

|   |   | 1 | 0 | 1 | 1 | 1 | 0 | 0 | 0 |              |

|   | 1 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 |              |

| 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | Final        |

Fractional digits in the final product=Fractional digits in multiplicand +Fractional digits in multiplier =  $2+2=4 \rightarrow (101.11)_2 \times (110.01)_2 = (100011.1111)_2$

#### **Binary Division**

Rules for Binary Division are:

| No. | Rule           |  |  |  |  |  |

|-----|----------------|--|--|--|--|--|

| 1   | $0 \div 1 = 0$ |  |  |  |  |  |

| 2   | $1 \div 1 = 1$ |  |  |  |  |  |

Divide  $(11011011)_2$  by  $(110)_2$

|   |   |   | 1 | 0 | 0 | 1 | 0 | 0 |   |   |

|---|---|---|---|---|---|---|---|---|---|---|

| 1 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | 1 |

|   |   |   | 1 | 1 | 0 |   |   |   |   |   |

|   |   |   | ( | 0 | 0 | 1 | 1 | 0 |   |   |

|   |   |   |   |   |   | 1 | 1 | 0 |   |   |

|   |   |   |   |   |   | 0 | 0 | 0 | 1 | 1 |

|   |   |   |   |   |   |   |   |   |   |   |

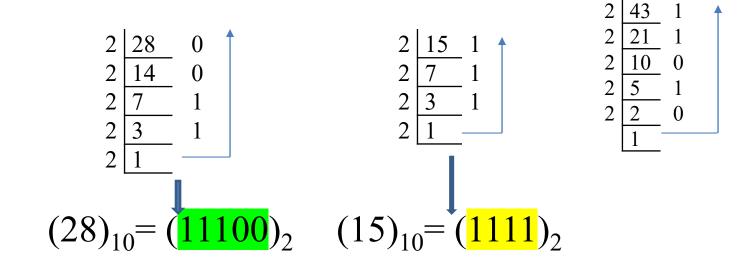

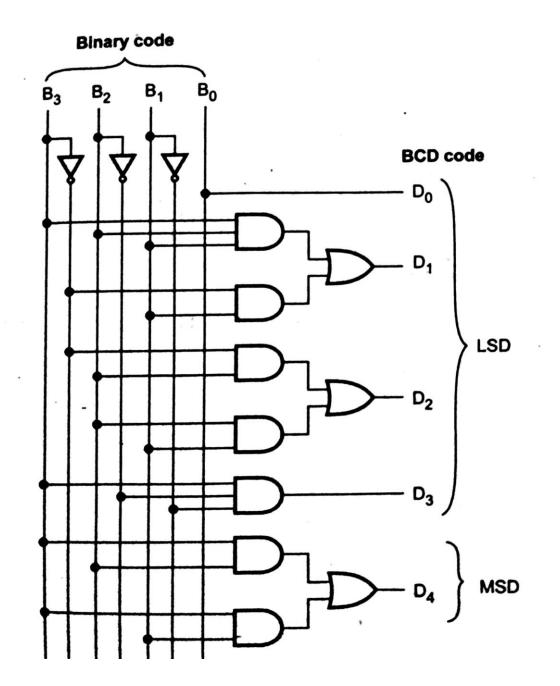

#### **Binary Codes**

- When numbers, alphabets or words are represented by a specific group of symbols i.e., they are encoded

- The group of symbols used to encode them is called codes. The digital data is represented, stored and transmitted as groups of binary digits (bits)

- Group of bits--- binary code---- numeric and alphanumeric code

#### Classification of binary codes

#### Weighted codes:

- In weighted codes, each digit position of the number represents a specific weight

- Examples:  $93 \rightarrow (1001)(0011) \rightarrow 8421$  code  $93 \rightarrow (1100)(0011) \rightarrow 5421$  code

#### Non-weighted codes :

- Non-weighted codes are not assigned with any weight to each digit position, i.e., each digit position within the number is not assigned fixed value

- Excess-3 and gray codes are the non-weighted codes

#### Reflective codes:

- A code is said to be reflective when the code for 9 is the complement for 0, the code for 8 is complement for 1, 7 for 2,6 for 3 and 5 for 4.

- Like 2421, codes 5211 and excess-3 are also reflective.

- The 8421 code is not reflective

#### Sequential codes

- In sequential codes each succeeding code is one binary number greater than its preceding code.

- This greatly aids mathematical manipulation of data

- The 8421 and excess-3 are sequential, whereas the 2421 and 5211 codes are not sequential

#### Alphanumeric codes

- The codes which consists of both numbers and alphabetic characters are called alphanumeric codes.

- Most of these codes, however, also represent symbols and various instructions necessary for conveying intelligible information

- The most commonly used alphanumeric codes are: ASCII, EBCDIC and Hollerith code

#### Error detecting and correcting codes

- When the digital information in the binary form is transmitted from one circuit or system to another circuit or system an error may occur.

- This means the signal corresponding to 0 may change to 1 or vice-versa due to presence of noise

- To maintain data integrity between transmitter and receiver, extra bit or more than one bit are added in the data.

- These extra bits allow the detection and sometimes the correction of error in the data.

- The data along with the extra bit /bits form the code

- Codes which allow only error detection are called error detecting codes and codes which allow error detection and correction are called error detecting and correcting codes

#### BCD(Binary Coded Decimal) codes

- BCD is a numeric code in which each digit of a decimal number is represented by a separate group of 4-bits.

| Decimal | BCD Code |

|---------|----------|

| 0       | 0000     |

| 1       | 0001     |

| 2       | 0010     |

| 3       | 0011     |

| 4       | 0100     |

| 5       | 0101     |

| 6       | 0110     |

| 7       | 0111     |

| 8       | 1000     |

| 9       | 1001     |

| 5    | 8    | Decimal     |

|------|------|-------------|

| 0101 | 1000 | BCD<br>Code |

#### **Advantages:**

• Easy to convert between it and decimal

#### **Disadvantages:**

- Less efficient

- Arithmetic operations are more complex

#### • Excess-3 code

- The excess-3 code can be derived from the natural BCD code by adding 3 to each coded number.

- It is a non-weighted code

- It is a sequential code

In excess-3 code we get 9's complement of a number by just complementing each bit. Due to this excess-3 code is called self-

complementing code or reflective code.

| Decimal | Excess-3 code |

|---------|---------------|

| 0       | 0011          |

| 1       | 0100          |

| 2       | 0101          |

| 3       | 0110          |

| 4       | 0111          |

| 5       | 1000          |

| 6       | 1001          |

| 7       | 1010          |

| 8       | 1011          |

| 9       | 1100          |

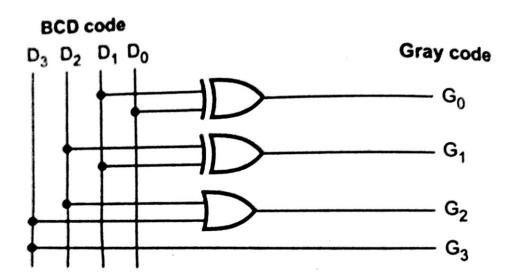

#### • Gary code

- Gray code is a non-weighted code and is a special case of unit-distance code

- In unit distance code, bit patterns for two consecutive numbers differ in only one bit position.

- These codes are also called as cyclic codes.

- The gray code is also called reflected code.

#### **Application of Gray code**

- Let us consider an application where 3-bit binary code is provided to indicate position of the rotating disk with the help of brushes.

- If one brush is slightly ahead of the other, an 180° error occur in the disk position.

- When the gray code is used to represent disk position then error due to improper brush alignment can be reduced. This is because the gray code assures that only one bit will change each time the decimal number is incremented.

- In 3-bit code probability of error is reduced upto 66% and in 4-bit code it is reduced upto 75%. This is an advantage of gray code.

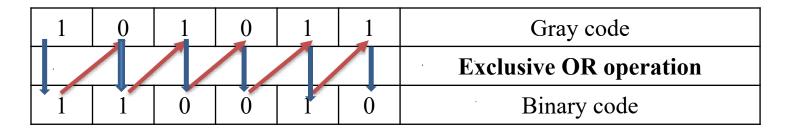

#### **Gray to Binary Conversion:**

#### **Exclusive OR operation**

| Α | В | А⊕В |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 0   |

#### Convert gray code 101011 into its binary equivalent.

$$(101011)_{\text{gray}} = (110010)_2$$

#### Binary to Gray code:

Convert 10111011 in binary into its equivalent gray code.

Exclusive OR operation

1 1 1 0 0 1 1 0 Gray code

#### **BCD** Addition

Case 1: Sum equals 9 or less with carry 0

Addition of 3 and 6 in BCD

|   | 1 | 1 |   |   | Carry     |

|---|---|---|---|---|-----------|

|   | 0 | 1 | 1 | 0 | BCD for 6 |

| + | 0 | 0 | 1 | 1 | BCD for 3 |

|   | 1 | 0 | 0 | 1 | BCD for 9 |

BCD for 14

#### Case 2: Sum greater than 9 with carry 0

|   | 0 | 1 | 1 | 0 | BCD for 6               |

|---|---|---|---|---|-------------------------|

| + | 1 | 0 | 0 | 0 | BCD for 8               |

|   | 1 | 1 | 1 | 0 | Invalid BCD number (14) |

|   |   |   |   |   |                         |

|   | 1 | 1 | 1 | 0 | Invalid BCD number (14) |

|   | 0 | 1 | 1 | 0 | Add 6 for correction    |

| 1 | 0 | 1 | 0 | 0 | Answer                  |

#### • Case 3: Sum greater than 9 with carry 0

|   |   |   |   |   | Carry                |

|---|---|---|---|---|----------------------|

|   | 1 | 0 | 0 | 0 | BCD for 8            |

| + | 1 | 0 | 0 | 1 | BCD for 9            |

| 1 | 0 | 0 | 0 | 1 | Incorrect BCD number |

|   |   |   |   |   |                      |

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | Incorrect BCD number |

|---|---|---|---|---|---|---|---|----------------------|

| 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | Add 6 for correction |

| 0 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | Answer               |

| 0 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | BCD for 17 |

|---|---|---|---|---|---|---|---|------------|

|---|---|---|---|---|---|---|---|------------|

BCD Subtraction using 9's complement

Perform  $(46)_{10}$ – $(22)_{10}$  in BCD using 9's complement.

Step 1: Find 9's complement of 22

9's complement of 22=(99-22)=77

Step 2:Add 46 and 9's complement of 22

|   | 1 |       |      |      | 1    | 1     |        |        | Carry                |

|---|---|-------|------|------|------|-------|--------|--------|----------------------|

|   | 0 | 1     | 0    | 0    | 0    | 1     | 1      | 0      | BCD of 46            |

| + | 0 | 1     | 1    | 1    | 0    | 1     | 1      | 1      | BCD of 77            |

|   | 1 | 0     | 1    | 1    | 1    | 1     | 0      | 1      | Invalid BCD numbers  |

|   |   |       |      |      |      |       |        |        |                      |

|   | 1 | 0     | 1    | 1    | 1    | 1     | 0      | 1      | Invalid BCD numbers  |

| + | 0 | 1     | 1    | 0    | 0    | 1     | 1      | 0      | Add 6 in each digit  |

| 1 | 0 | 0     | 1    | 0    | 0    | 0     | 1      | 1      |                      |

|   |   |       |      |      |      |       |        | 1      | Add end around carry |

|   | 0 | 0     | 1    | 0    | 0    | 1     | 0      | 0      | Result (BCD of 24)   |

|   |   | Since | ther | e is | carr | y the | e resu | ult is | positive and true    |

BCD Subtraction using 9's complement

Perform  $(24)_{10}$ – $(56)_{10}$  in BCD using 9's complement.

Step 1: Find 9's complement of 56

9's complement of 56=(99-56)=43

Step 2:Add 24 and 9's complement of 56

|   |                                         |   |   |   |   |   |   |   | Carry     |  |

|---|-----------------------------------------|---|---|---|---|---|---|---|-----------|--|

|   | 0                                       | 0 | 1 | 0 | 0 | 1 | 0 | 0 | BCD of 24 |  |

| + | 0                                       | 1 | 0 | 0 | 0 | 0 | 1 | 1 | BCD of 43 |  |

|   | 0                                       | 1 | 1 | 0 | 0 | 1 | 1 | 1 | BCD of 67 |  |

|   | Since there is 0 the result is negative |   |   |   |   |   |   |   |           |  |

Step 3: Take 9's complement of answer

BCD Subtraction using 10's complement

Perform  $(46)_{10}$ – $(22)_{10}$  in BCD using 9's complement.

Step 1: Find 10's complement of 22

10's complement of 22=9's complement of 22+1 = (99-22)+1=78

Step 2:Add 46 and 10's complement of 22

|   | 1                                                    |   |   |   |   |      |        |       | Carry               |  |  |

|---|------------------------------------------------------|---|---|---|---|------|--------|-------|---------------------|--|--|

|   | 0                                                    | 1 | 0 | 0 | 0 | 1    | 1      | 0     | BCD of 46           |  |  |

| + | 0                                                    | 1 | 1 | 1 | 1 | 0    | 0      | 0     | BCD of 78           |  |  |

|   | 1                                                    | 0 | 1 | 1 | 1 | 1    | 1      | 0     | Invalid BCD numbers |  |  |

|   |                                                      |   |   |   |   |      |        |       |                     |  |  |

|   | 1                                                    | 0 | 1 | 1 | 1 | 1    | 1      | 0     | Invalid BCD numbers |  |  |

| + | 0                                                    | 1 | 1 | 0 | 0 | 1    | 1      | 0     | Add 6 in each digit |  |  |

| 1 | 0                                                    | 0 | 1 | 0 | 0 | 1    | 0      | 0     |                     |  |  |

|   |                                                      |   |   |   | C | arry | is ign | nored |                     |  |  |

|   | 0                                                    | 0 | 1 | 0 | 0 | 1    | 0      | 0     | Result (BCD of 24)  |  |  |

|   | Since there is carry the result is positive and true |   |   |   |   |      |        |       |                     |  |  |

BCD Subtraction using 10's complement

Perform  $(24)_{10}$ – $(56)_{10}$  in BCD using 10's complement.

Step 1: Find 10's complement of 56

9's complement of 56=(99-56)+1=44

Step 2:Add 24 and 10's complement of 56

|   |                                         |   |   |   |   |   |   |   | Carry     |  |

|---|-----------------------------------------|---|---|---|---|---|---|---|-----------|--|

|   | 0                                       | 0 | 1 | 0 | 0 | 1 | 0 | 0 | BCD of 24 |  |

| + | 0                                       | 1 | 0 | 0 | 0 | 1 | 0 | 0 | BCD of 44 |  |

|   | 0                                       | 1 | 1 | 0 | 1 | 0 | 0 | 0 | BCD of 68 |  |

|   | Since there is 0 the result is negative |   |   |   |   |   |   |   |           |  |

Step 3: Take 10's complement of answer

$$(99-68)+1=32 \rightarrow 24-56=32$$

#### **Excess-3 Addition:**

# a)Carry is generated:8+6

|   | 1 | 0 | 1 | 1 | Excess-3 for 8 |

|---|---|---|---|---|----------------|

| + | 1 | 0 | 0 | 1 | Excess-3 for 6 |

| 1 | 0 | 1 | 0 | 0 | Carry is 1     |

| 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 |                          |

|---|---|---|---|---|---|---|---|--------------------------|

| 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | Add 3                    |

| 0 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | Result (Excess-3 for 14) |

|   | ] |   |   |   | 4 |   |   | Result in decimal        |

|   |   |   |   |   |   |   |   |                          |

#### **Excess-3 Addition:**

## a)Carry is not generated:1+2

|   | 0 | 1 | 0 | 0 | Excess-3 for 1 |

|---|---|---|---|---|----------------|

| + | 0 | 1 | 0 | 1 | Excess-3 for 2 |

| 0 | 1 | 0 | 0 | 1 | Carry is 0     |

| 0 | 1 | 0 | 0 | 1 |                         |

|---|---|---|---|---|-------------------------|

|   | 0 | 0 | 1 | 1 | Sub 3                   |

|   | 0 | 1 | 1 | 0 | Result (Excess-3 for 3) |

| 3 |   |   |   |   | Result in decimal       |

#### **Excess-3 Subtraction:**

# a)Carry is generated:8-5

| 1 | 0 | 0 | 0 | Excess-3 for 5 |

|---|---|---|---|----------------|

| 0 | 1 | 1 | 1 | Complement     |

|   | 1 | 0 | 1 | 1 | Excess-3 for 8              |

|---|---|---|---|---|-----------------------------|

| + | 0 | 1 | 1 | 1 | Complement of 5 in Excess-3 |

| 1 | 0 | 0 | 1 | 0 | Carry is 1                  |

| 1 | 0 | 0 | 1 | 0 |                         |

|---|---|---|---|---|-------------------------|

|   | 0 | 0 | 1 | 1 | Add 3                   |

| 1 | 0 | 1 | 0 | 1 | Result (Excess-3 for 3) |

|   |   |   |   | 1 | Add end-around carry    |

|   | 0 | 1 | 1 | 0 | Excess-3 for 3          |

#### **Excess-3 Subtraction:**

## a) Carry is not generated: 5-8

| 1 | 0 | 1 | 1 | Excess-3 for 8 |

|---|---|---|---|----------------|

| 0 | 1 | 0 | 0 | Complement     |

|   | 1 | 0 | 0 | 0 | Excess-3 for 5              |  |

|---|---|---|---|---|-----------------------------|--|

| + | 0 | 1 | 0 | 0 | Complement of 8 in Excess-3 |  |

| 0 | 1 | 1 | 0 | 0 | Carry is 0                  |  |

| 0 | 1 | 1 | 0 | 0 |                         |

|---|---|---|---|---|-------------------------|

|   | 0 | 0 | 1 | 1 | Sub 3                   |

| 0 | 1 | 0 | 0 | 1 | Result (Excess-3 for 3) |

### **Boolean Algebra**

- Boolean algebra is a mathematical system that defines a series of logical operations (AND,OR,NOT) performed on sets of variables (a,b,c,...).

- When stated in this form, the expression is called a Boolean equation or switching equation.

#### **Terminologies:**

Variable: The symbol which represent an arbitrary elements of an Boolean algebra is known as variable.

Any single variable or a function of several variables can have either a 1 or 0 value.

**Constant:** In expression Y=A+1, the first term A is a variable and the second term has a fixed value 1. So 1 is a constant here. The constant may be 1 or 0.

**Complement:** A complement of a variable is presented by a "bar" over the letter and sometimes denoted by (`).

Example:  $\overline{A}$  is the complement of the variable A, if  $A=0 \rightarrow \overline{A} = 1$  and  $A=1 \rightarrow \overline{A} = 0$

**Literal:** Each occurrence of a variable in Boolean function either in a complemented or an uncomplemented form is called a literal.

**Boolean Function:** Boolean expressions are constructed by connecting the Boolean constants and variables with the Boolean operations. These Boolean expressions are also known as Boolean formulae.

We use Boolean expressions to describe the Boolean functions.

Example:  $f(A,B,C) = (A + \overline{B})C$

#### **Properties of Boolean Algebra**

#### Closure Property

Closure(a): Closure with respect to operator +: when two binary elements are operated by operator +, the result is a unique binary element.

Closure(b):Closure with respect to operator .(dot): when two binary elements are operated by operator .(dot), the result is a unique binary element.

• Identity property: A.1=1.A=A

Commutative property

Commutative with respect to +: A+B=B+A

Commutative with respect to . : A.B=B.A

Distributive property

Associative property

$$A+(B+C)=(A+B)+C$$

$$(A.B).C=A(B.C)$$

Complement property

$$A.\overline{A}=0$$

$A+\overline{A}=1$

Idempotency property

$$A.A=A$$

$A+A=A$

Absorption property

Involution property

$$=$$

$A=A$

# De Morgan's Theorem

#### Theorom:1

the complement of the product of all the terms is equal to the sum of the complement of each term.

#### Theorom:2

the complement of the sum of all the terms is equal to the product of the complement of each term.

#### De-Morgan's theorem

| A | В | $\overline{AB}$ | $\overline{A}+\overline{B}$ |

|---|---|-----------------|-----------------------------|

| 0 | 0 | 1               | 1                           |

| 0 | 1 | 1               | 1                           |

| 1 | 0 | 1               | 1                           |

| 1 | 1 | 0               | 0                           |

| A | В | $\overline{A+B}$ | $\overline{A}$ . $\overline{B}$ |

|---|---|------------------|---------------------------------|

| 0 | 0 | 1                | 1                               |

| 0 | 1 | 0                | 0                               |

| 1 | 0 | 0                | 0                               |

| 1 | 1 | 0                | 0                               |

#### Principle of duality:

- The principle of duality theorem says that, starting with a Boolean relation, we can derive another Boolean relation by,

- Changing the OR sign to an AND sign

- Changing each AND sign to an OR sign and

- Complementing any 0 or 1 appearing in the expression.

- Dual of relation  $\rightarrow$  A+ $\overline{A}$ =1 is A. $\overline{A}$ =0

- Consensus Law:

- In simplification of Boolean expression, an expression of the form  $AB+\overline{A}C+BC$  the term BC is redundant and can be eliminated to form the equivalent expression  $AB+\overline{A}C$ . The theorem used for this simplification is known as consensus theorem and it is stated as

$$AB+\overline{A}C+BC=AB+\overline{A}C$$

Proof:

$$AB+\overline{A}C+BC=AB+\overline{A}C+(A+\overline{A})BC$$

$$=AB+\overline{A}C+ABC+\overline{A}BC$$

$$=AB(1+C)+\overline{A}C(1+B)$$

$$=AB+\overline{A}C$$

Prove the following Boolean identities

$$(x_{1}+x_{2})(\overline{x_{1}} \ \overline{x_{3}} + x_{3}) (\overline{x_{2}} + x_{1}x_{3}) = \overline{x_{1}}x_{2}$$

$$(x_{1}+x_{2})(\overline{x_{1}} \ \overline{x_{3}} + x_{3}) (\overline{x_{2}} + x_{1}x_{3})$$

$$= (x_{1}+x_{2})(\overline{x_{1}} \ \overline{x_{3}} + x_{3}) (\overline{x_{2}} \cdot x_{1}x_{3})$$

$$= (x_{1}+x_{2})(\overline{x_{1}} \ \overline{x_{3}} + x_{3}) (x_{2} \cdot (\overline{x_{1}} + \overline{x_{3}}))$$

$$= (x_{1}+x_{2})(\overline{x_{1}} \ \overline{x_{3}} + x_{3}) (x_{2} \ \overline{x_{1}} + x_{2}\overline{x_{3}})$$

$$= (x_{1}+x_{2})(\overline{x_{1}} + x_{3}) (x_{2} \ \overline{x_{1}} + x_{2}\overline{x_{3}}) (\operatorname{since } A + \overline{A}B = A + B)$$

$$= (x_{1}+x_{2})(\overline{x_{1}} + x_{3}) (x_{2} \ \overline{x_{1}} + x_{2}x_{3}) (x_{2} \ \overline{x_{1}} + x_{2}\overline{x_{3}})$$

$$= (x_{1}+x_{2})(\overline{x_{1}} + x_{3}) (x_{2} \ \overline{x_{1}} + x_{2}x_{3}) (x_{2} \ \overline{x_{1}} + x_{2}\overline{x_{3}})$$

$$= (x_{1}+x_{2})(\overline{x_{1}} + x_{3}) (x_{2} \ \overline{x_{1}} + x_{2}x_{3}) (x_{2} \ \overline{x_{1}} + x_{2}\overline{x_{3}})$$

$$= (x_{1}+x_{2})(\overline{x_{1}} + x_{3}) (x_{2} \ \overline{x_{1}} + x_{2}x_{3}) (x_{2} \ \overline{x_{1}} + x_{2}\overline{x_{3}})$$

$$= (x_{1}+x_{2})(\overline{x_{1}} + x_{3}) (x_{2} \ \overline{x_{1}} + x_{2}x_{3}) (x_{2} \ \overline{x_{1}} + x_{2}\overline{x_{3}})$$

$$= (x_{1}+x_{2})(\overline{x_{1}} + x_{3}) (x_{2} \ \overline{x_{1}} + x_{2}x_{3}) (x_{2} \ \overline{x_{1}} + x_{2}\overline{x_{3}})$$

$$= (x_{1}+x_{2})(\overline{x_{1}} + x_{3}) (x_{2} \ \overline{x_{1}} + x_{2}x_{3}) (x_{2} \ \overline{x_{1}} + x_{2}\overline{x_{3}})$$

$$= (x_{1}+x_{2})(\overline{x_{1}} + x_{3}) (x_{2} \ \overline{x_{1}} + x_{2}\overline{x_{3}}) (x_{2} \ \overline{x_{1}} + x_{2}\overline{x_{3}})$$

$$= (x_{1}+x_{2})(\overline{x_{1}} + x_{2}x_{3}) (x_{2} \ \overline{x_{1}} + x_{2}\overline{x_{3}}) (x_{2} \ \overline{x_{1}} + x_{2}\overline{x_{3}})$$

$$= (x_{1}+x_{2})(\overline{x_{1}} + x_{2}x_{3}) (x_{2} \ \overline{x_{1}} + x_{2}\overline{x_{3}}) (x_{2} \ \overline{x_{1}} + x_{2}\overline{x_{3}})$$

$$= (x_{1}+x_{2})(\overline{x_{1}} + x_{2}x_{3}) (x_{2} \ \overline{x_{1}} + x_{2}\overline{x_{3}}) (x_{2} \ \overline{x_{1}} + x_{2}\overline{x_{3}})$$

$$= (x_{1}+x_{2})(\overline{x_{1}} + x_{2}x_{3}) (x_{2} \ \overline{x_{1}} + x_{2}\overline{x_{3}}) (x_{2} \ \overline{x_{1}} + x_{2}\overline{x_{3}})$$

$$= (x_{1}+x_{2})(\overline{x_{1}} + x_{2}x_{3}) (x_{2} \ \overline{x_{1}} + x_{2}\overline{x_{3}}) (x_{2} \ \overline{x_{1}} + x_{2}\overline{x_{3}})$$

$$= (x_{1}+x_{2})(\overline{x_{1}} + x_{2}x_{3}) (x_{2} \ \overline{x_{1}} + x_{2}x_{3}) (x_{2} \ \overline{x_{1}} + x_{2}\overline{x_{3}})$$

$$= (x_{1}+x_{2})(\overline{x_{1}} + x_{2}x_{3}) (x_{2} \ \overline{x_{1}} + x_{2}x_{$$

• Prove the following using DeMorgan's theorem

$$[(x + y)' + (x + y)']' = x + y$$

$$= (\overline{(x+y)} + \overline{(x+y)})$$

$$= \overline{(x+y)} \cdot \overline{(x+y)}$$

$$= (x+y) \cdot (x+y)$$

$$= (x+y) \cdot (x+y)$$

# **Boolean expression**

• Boolean expressions are constructed by connecting the Boolean constants and variables with the Boolean operations.

$$f(A,B,C,D) = A + \overline{B}C + AC\overline{D}$$

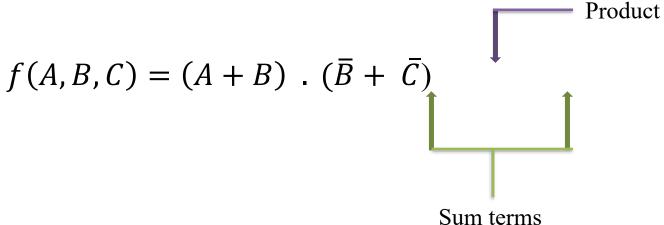

Sum of Product form:(SOP)

$$f(A,B,C) = AC + A\overline{B}\overline{C}$$

Also known as disjunctive normal form or disjunctive normal formula

$$f(P,Q,R,S) = \overline{P}Q + QR + RS$$

Product Terms

Product Terms

• Product of Sum form (POS)

Conjunctive normal formula or conjunctive normal form

$$f(P,Q,R,S) = (\overline{P} + Q) \cdot (Q + R) \cdot (R + S)$$

Sum terms

# Standard (Canonical) SOP & Standard (Canonical) POS Form

- If each term in the SOP form contains all the literals then the SOP form is known as **standard or canonical SOP form.**

- Each individual term in the standard SOP form is called minterm.

$$f(A,B,C) = ABC + A\bar{B}\bar{C} + A\bar{B}C$$

- If each term in POS form contains all the literals then the POS form is known as **standard or canonical POS form.**

- Each individual term in the standard SOP form is called **maxterm**.

$$f(A, B, C) = (A + B + C) \cdot (A + \overline{B} + \overline{C})$$

#### **Converting Expressions in Standard SOP form**

Step 1: Find the missing literal in each product term if any.

Step 2:AND each product term having missing literal(s) with term(s) form by ORing the literal and its complement.

Step 3:Expand the terms by applying distributive law and reorder the literals in the product terms.

Step 4:Reduce the expression by omitting the repeated product terms if any.

Example: Convert the given expression in standard SOP form.

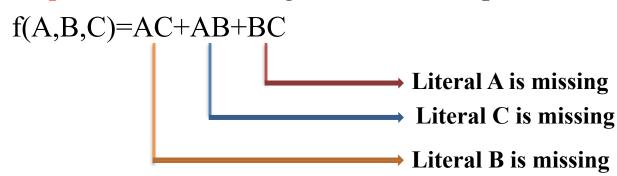

$$f(A,B,C)=AC+AB+BC$$

Solution:

Step 1: Find the missing literals in each product term

Step 2: AND product term with missing (literal + its complement)

Step 3:Expand the terms and reorder the literals

Expand:

$$f(A,B,C)=ACB + AC\overline{B} + ABC + AB\overline{C} + BCA + BC\overline{A}$$

Reorder:

$$f(A,B,C)=ABC+A\overline{B}C+ABC+AB\overline{C}+ABC+\overline{A}BC$$

Step 4: Omit repeated product terms

$$f(A,B,C) = \overline{ABC} + A\overline{B}C + \overline{ABC} +$$

#### **Converting Expressions in Standard POS form**

Step 1: Find the missing literal in each sum term if any.

Step 2:OR each sum term having missing literal(s) with term(s) form by ANDing the literal and its complement.

Step 3:Expand the terms by applying distributive law and reorder the literals in the sum terms.

Step 4:Reduce the expression by omitting the repeated sum terms if any.

Example: Convert the given expression in standard POS form. Y=A.

(A+B+C)

Solution:

Step 1: Find the missing literals in each sum term

Step 2: OR sum term with (missing literal . its complement)  $Y = [A + (B, \overline{B}) + (C, \overline{C})] \cdot (A + B + C)$

Step 3: Expand the terms and reorder literals

$$Y=(A+B).(A+\overline{B})+(C.\overline{C})$$

].  $(A+B+C)$

$$Y=(A+B+C).(A+\overline{B}+C).(A+B+\overline{C}).(A+\overline{B}+\overline{C}).(A+B+C)$$

Step 4: Omit repeated sum terms

Y=

$$(A+B+C)$$

.  $(A+\overline{B}+C)$ .  $(A+B+\overline{C})$ .  $(A+\overline{B}+\overline{C})$ .  $(A+B+C)$

Y= $(A+B+C)$ .  $(A+\overline{B}+C)$ .  $(A+B+\overline{C})$ .  $(A+\overline{B}+\overline{C})$

#### **M Notations: Minterms and Maxterms**

- Each individual term in standard SOP form is called **minterm** and each individual term in standard POS form is called **maxterm**.

- In general, for a n-variable logical function there are 2<sup>n</sup> minterms and an equal number of maxterms.

- Each minterm is represented by m<sub>i</sub> and each maxterm is represented by M<sub>i</sub>, where the subscript i is the decimal number equivalent of the natural binary number.

- $\Sigma$ ,  $m_i \rightarrow$  denotes sum of product form(SOP)

- $\Pi, M_i \rightarrow$  denotes product of sum form(POS)

#### Minterms and Maxterms for three variables

| Decimal | Variables |       | es    | Minterms<br>(SOP)                          | Maxterms (POS)                                              |

|---------|-----------|-------|-------|--------------------------------------------|-------------------------------------------------------------|

|         | A<br>(4)  | B (2) | C (1) | $m_{i}$                                    | $M_{\rm i}$                                                 |

| 0       | 0         | 0     | 0     | $\overline{A}\overline{B}\overline{C}=m_0$ | $A+B+C=M_0$                                                 |

| 1       | 0         | 0     | 1     | $\overline{A}\overline{B}$ C= $m_1$        | $A+B+\bar{C}=M_I$                                           |

| 2       | 0         | 1     | 0     | Ā B <b>C</b> =m <sub>2</sub>               | $A + \overline{B} + C = M_2$                                |

| 3       | 0         | 1     | 1     | Ā BC=m <sub>3</sub>                        | $A + \bar{B} + \bar{C} = M_3$                               |

| 4       | 1         | 0     | 0     | $A\overline{B} \overline{C}=m_4$           | $\bar{A} + B + C = M_4$                                     |

| 5       | 1         | 0     | 1     | $A\overline{B} C=m_5$                      | $\bar{A} + B + \bar{C} = M_5$                               |

| 6       | 1         | 1     | 0     | AB¯C=m <sub>6</sub>                        | $\bar{A} + \bar{B} + C$                                     |

|         |           |       |       |                                            | $=M_6$                                                      |

| 7       | 1         | 1     | 1     | ABC=m <sub>7</sub>                         | $egin{aligned} ar{A} + ar{B} + ar{C} \ = M_7 \end{aligned}$ |

Minterms and Maxterms for four variables

| Decimal |   | Varia | bles |   | Minterms       | Maxterms |

|---------|---|-------|------|---|----------------|----------|

|         | A | В     | С    | D | m <sub>i</sub> | $M_{i}$  |

| 0       | 0 | 0     | 0    | 0 |                |          |

| 1       |   |       |      |   |                |          |

| 2       |   |       |      |   |                |          |

| 3       |   |       |      |   |                |          |

| 4       |   |       |      |   |                |          |

| 5       |   |       |      |   |                |          |

| 6       |   |       |      |   |                |          |

| 7       |   |       |      |   |                |          |

| 8       |   |       |      |   |                |          |

| 9       |   |       |      |   |                |          |

| 10      | 1 | 0     | 1    | 0 |                |          |

| 11      |   |       |      |   |                |          |

| 12      |   |       |      |   |                |          |

| 13      |   |       |      |   |                |          |

| 14      |   |       |      |   |                |          |

| 15      | 1 | 1     | 1    | 1 |                |          |

#### Examples:

$$f(A,B,C)=ABC + A \overline{B}C + AB \overline{C} + \overline{A}BC$$

$$= m_7 + m_5 + m_6 + m_3$$

$$= \Sigma m(3,5,6,7)$$

$$Y=(A+B+C). (A+\overline{B}+C). (A+B+\overline{C}). (A+\overline{B}+\overline{C})$$

$$= M_0. M_2. M_1. M_3$$

$$= \pi M(0,1,2,3)$$

Complements of Standard Forms:

$$f(A,B,C) = m_7 + m_5 + m_6 + m_3 = M_0 \cdot M_1 \cdot M_2 \cdot M_4$$

$f(A,B,C) = \sum m(3,5,6,7) = \pi M(0,1,2,4)$

In case of four variables,

$$f(A,B,C,D) = \Sigma m(0,2,3,5,6,7,11,13,14) = \pi M(1,4,8,9,10,12,15)$$

Express F=A+B'C as sum of minterms.

Solution:

$$A + \bar{B}C = A(B + \bar{B})(C + \bar{C}) + (A + \bar{A})\bar{B}C$$

$$= (AB + A\bar{B})(C + \bar{C}) + (A\bar{B}C + \bar{A}\bar{B}C)$$

$$= ABC + A\bar{B}C + AB\bar{C} + A\bar{B}\bar{C} + A\bar{B}C + \bar{A}\bar{B}C$$

$$= \Sigma m(7,5,6,4,5,1)$$

$$= \Sigma m(1,4,5,6,7)$$

Express the following F=XY+X'Z in product of maxterm.

# K-map Minimization

- During the process of simplification of Boolean expression we have to predict each successive step

- We can never be absolutely certain that an expression simplified by Boolean algebra alone is the simplest possible expression

- On the other hand, the map method gives us a systematic approach for simplifying a Boolean expression

- The map method, first proposed by Veitch and modified by Karnaugh, hence it is known as the Veitch diagram or the Karnaugh map.

# **Advantages of K-Maps**

- The K-map simplification technique is simpler and less error-prone compared to the method of solving the logical expressions using Boolean laws.

- It prevents the need to remember each and every Boolean algebraic theorem.

- It involves fewer steps than the algebraic minimization technique to arrive at a simplified expression.

- K-map simplification technique always results in minimum expression if carried out properly.

# MINIMIZATION

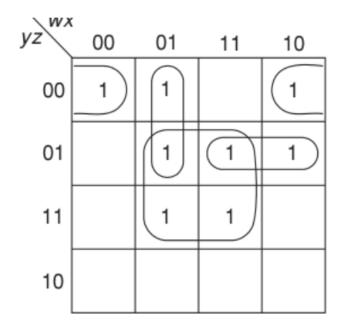

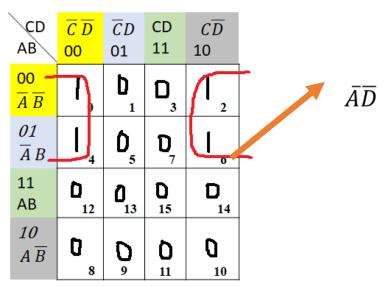

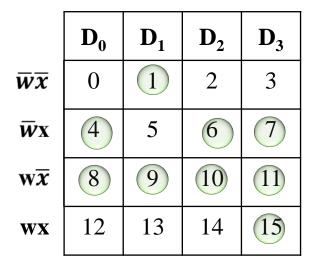

Example: Two irredundant expressions for  $f(w,x,y,z) = \sum (0,4,5,7,8,9,13,15)$

(a) f = x'y'z' + w'xy' + wy'z + xz is an irredundant expression.

(b) f = w'y'z' + wx'y' + xz is the unique minimal expression.

# **MINIMIZATION**

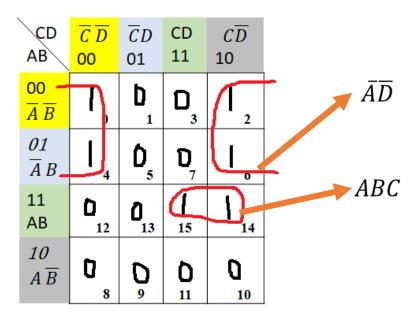

Example:  $f(w,x,y,z) = \sum (1,5,6,7,11,12,13,15)$

Only one irredundant form: f = wxy' + wyz + w'xy + w'y'zDotted cube xz is redundant

| yz wx | 00 | 01 | 11  | 10 |

|-------|----|----|-----|----|

| 00    |    |    | 1   |    |

| 01    | 1  | 11 | 1   |    |

| 11    |    | 1  | 1 , | 1  |

| 10    |    | 1  |     |    |

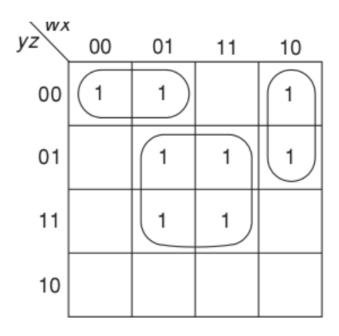

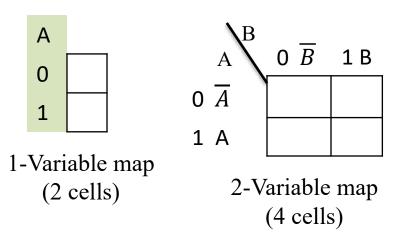

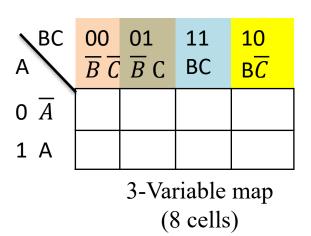

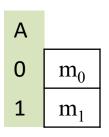

#### One-Variable, Two-Variable, Three-Variable and Four-Variable Maps

- The basis of this method is a graphical chart known as Karnaugh map (K-map)

- It contains boxes called cells.

- Each of the cell represents one of the 2<sup>n</sup> possible products that can be formed from n variables.

- Thus, a 2-variable map contains  $2^2 = 4$  cells, a 3-variable map contains  $2^3 = 8$  cells and so forth.

# 4-variable map (16 cells)

| CD<br>AB                    | $\overline{C}\overline{D}$ | <i>C D</i> 01 | CD<br>11 | <i>CD</i> 10 |

|-----------------------------|----------------------------|---------------|----------|--------------|

| $\frac{00}{A} \frac{B}{B}$  |                            |               |          |              |

| $\frac{\partial 1}{A B}$    |                            |               |          |              |

| 11<br>AB                    |                            |               |          |              |

| $\frac{10}{A \overline{B}}$ |                            |               |          |              |

## One-Variable, Two-Variable, Three-Variable and Four-Variable Maps

# Representation:

1-Variable map (2 cells)

| $A^{B}$          | 0 <i>B</i> | 1 B            |

|------------------|------------|----------------|

| $0 \overline{A}$ | $m_0$      | $\mathbf{m}_1$ |

| 1 A              | $m_2$      | $m_3$          |

|                  |            |                |

2-Variable map (4 cells)

| A BC            |       | 01<br>$\overline{B}$ C | 11<br>BC | 10<br>в <u>С</u> |

|-----------------|-------|------------------------|----------|------------------|

| $o\overline{A}$ | $m_0$ | $\mathbf{m}_1$         | $m_3$    | $m_2$            |

| 1 A             | $m_4$ | $m_5$                  | $m_7$    | $m_6$            |

3-Variable map (8 cells)

| Α |   |

|---|---|

| 0 | 0 |

| 1 | 1 |

| AB               | 0 <u>B</u> | 1 B |

|------------------|------------|-----|

| $o \overline{A}$ | 0          | 1   |

| 1 A              | 2          | 3   |

| A BC             |   | 01<br><del>B</del> C | 11<br>BC | 10<br>B <u>C</u> |

|------------------|---|----------------------|----------|------------------|

| $0 \overline{A}$ | 0 | 1                    | 3        | 2                |

| 1 A              | 4 | 5                    | 7        | 6                |

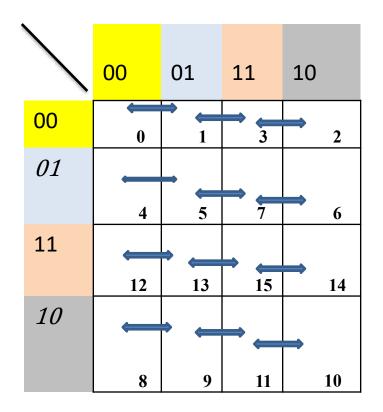

# 4-variable map (16 cells)

| CD<br>AB                                                   | <i>C D</i> 00   | <i>C D</i> 01   | CD<br>11        | <i>CD</i> 10    |

|------------------------------------------------------------|-----------------|-----------------|-----------------|-----------------|

| $\frac{00}{\overline{A}}\frac{\overline{B}}{\overline{B}}$ | $m_0$           | $\mathbf{m}_1$  | $m_3$           | $m_2$           |

| $\frac{\partial 1}{A B}$                                   | $m_4$           | $m_5$           | $\mathbf{m}_7$  | $m_6$           |

| 11<br>AB                                                   | m <sub>12</sub> | m <sub>13</sub> | m <sub>15</sub> | m <sub>14</sub> |

| $\frac{10}{A  \overline{B}}$                               | m <sub>8</sub>  | m <sub>9</sub>  | m <sub>11</sub> | m <sub>10</sub> |

| <b>€</b> D                  | $\overline{C} \overline{D}$ | $\overline{C}D$ | CD | $C\overline{D}$ |

|-----------------------------|-----------------------------|-----------------|----|-----------------|

| AB                          | 00                          | 01              | 11 | 10              |

| 00                          |                             |                 |    |                 |

| $\overline{A} \overline{B}$ | 0                           | 1               | 3  | 2               |

| 01                          |                             |                 |    |                 |

| $\overline{A} B$            | 4                           | 5               | 7  | 6               |

| 11                          |                             |                 |    |                 |

| AB                          | 12                          | 13              | 15 | 14              |

| 10                          |                             |                 |    |                 |

| $A \overline{B}$            |                             |                 |    |                 |

|                             | 8                           | 9               | 11 | 10              |

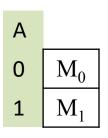

## One-Variable, Two-Variable, Three-Variable and Four-Variable Maps

# Representation(POS):

|   | $A^{\mathbf{B}}$ | 0 B                      | 1 $\overline{B}$         |

|---|------------------|--------------------------|--------------------------|

| 0 | Α `              | $M_0$                    | $\mathbf{M}_1$           |

| 1 | $\overline{A}$   | $M_2$                    | $M_3$                    |

| 1 | A                | 1 <b>v1</b> <sub>2</sub> | 1 <b>VI</b> <sub>3</sub> |

1 D

| Α |   |

|---|---|

| 0 | 0 |

| 1 | 1 |

$$\begin{array}{c|cccc}

A & OB & 1\overline{B} \\

O & A & & & \\

1 \overline{A} & & 2 & 3

\end{array}$$

| B+C              | 00<br>B + C | $01$ B+ $\overline{C}$ | $\frac{11}{B} + \overline{C}$ | $\frac{10}{B}$ +C |

|------------------|-------------|------------------------|-------------------------------|-------------------|

| 0 A              | $M_0$       | $M_1$                  | $M_3$                         | $M_2$             |

| 1 $\overline{A}$ | $M_4$       | $M_5$                  | $M_7$                         | $M_6$             |

3-Variable map (8 cells)

| VB+C             | 00    | 01               | 11                            | 10                |

|------------------|-------|------------------|-------------------------------|-------------------|

| A                | B + C | $B+\overline{C}$ | $\overline{B} + \overline{C}$ | $\overline{B}$ +C |

| 0 A              | 0     | 1                | 3                             | 2                 |

| 1 $\overline{A}$ | 4     | 5                | 7                             | 6                 |

# 4-variable map (16 cells)

| C+D<br>A+B                    | C+D<br>00       | $C + \overline{D}$ 01 | $\overline{C} + \overline{D}$ 11 | <del>C</del> +D<br>10 |

|-------------------------------|-----------------|-----------------------|----------------------------------|-----------------------|

| 00<br>A + B                   | $\mathbf{M}_0$  | $\mathbf{M}_1$        | $M_3$                            | $M_2$                 |

| $\frac{01}{A+\overline{B}}$   | $M_4$           | $M_5$                 | $M_7$                            | $M_6$                 |

| $\frac{11}{A} + \overline{B}$ | M <sub>12</sub> | M <sub>13</sub>       | M <sub>15</sub>                  | M <sub>14</sub>       |

| $\frac{10}{A}$ +B             | $M_8$           | $M_9$                 | M <sub>11</sub>                  | M <sub>10</sub>       |

| C+D<br>A+B                    | C+D<br>00 | $C + \overline{D}$<br>01 | $\overline{C} + \overline{D}$ 11 | <u>C</u> +D<br>10 |

|-------------------------------|-----------|--------------------------|----------------------------------|-------------------|

| $00 \\ A + B$                 | 0         | 1                        | 3                                | 2                 |

| $\frac{01}{A+\overline{B}}$   | 4         | 5                        | 7                                | 6                 |

| $\frac{11}{A} + \overline{B}$ |           |                          |                                  |                   |

|                               | 12        | 13                       | 15                               | 14                |

| 10                            |           |                          |                                  |                   |

| $\overline{A}$ +B             |           |                          |                                  |                   |

|                               | 8         | 9                        | 11                               | 10                |

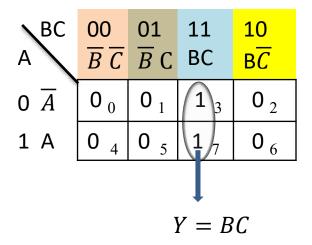

## Plotting a K-map

Cell: the smallest unit of a Karnaugh map, corresponding to one line of a truth table. The input variables are the cell's co-ordinates and the output variable is the cell's contents.

| No. | Inputs |   |   | Output |

|-----|--------|---|---|--------|

|     | A      | В | С | Y      |

| 0   | 0      | 0 | 0 | 0      |

| 1   | 0      | 0 | 1 | 1      |

| 2   | 0      | 1 | 0 | 0      |

| 3   | 0      | 1 | 1 | 0      |

| 4   | 1      | 0 | 0 | 1      |

| 5   | 1      | 0 | 1 | 1      |

| 6   | 1      | 1 | 0 | 0      |

| 7   | 1      | 1 | 1 | 1      |

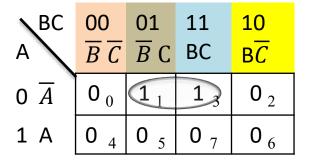

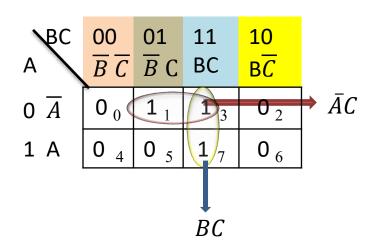

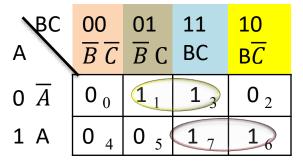

| BC<br>A         | 00<br><u>B</u> <u>C</u> | 01<br><del>B</del> C | 11<br>BC | 10<br>В <u>С</u> |

|-----------------|-------------------------|----------------------|----------|------------------|

| $0\overline{A}$ | 0 0                     | <b>1</b> 1           | 0 3      | 0 2              |

| 1 A             | 1 4                     | 1 5                  | 1 7      | 0 6              |

| No. |   | Inpu | Output |   |   |

|-----|---|------|--------|---|---|

|     | A | В    | C      | D | Y |

| 0   | 0 | 0    | 0      | 0 | 1 |

| 1   | 0 | 0    | 0      | 1 | 1 |

| 2   | 0 | 0    | 1      | 0 | 1 |

| 3   | 0 | 0    | 1      | 1 | 0 |

| 4   | 0 | 1    | 0      | 0 | 0 |

| 5   | 0 | 1    | 0      | 1 | 1 |

| 6   | 0 | 1    | 1      | 0 | 0 |

| 7   | 0 | 1    | 1      | 1 | 1 |

| 8   | 1 | 0    | 0      | 0 | 0 |

| 9   | 1 | 0    | 0      | 1 | 1 |

| 10  | 1 | 0    | 1      | 0 | 0 |

| 11  | 1 | 0    | 1      | 1 | 0 |

| 12  | 1 | 1    | 0      | 0 | 1 |

| 13  | 1 | 1    | 0      | 1 | 0 |

| 14  | 1 | 1    | 1      | 0 | 1 |

| 15  | 1 | 1    | 1      | 1 | 1 |

| CD<br>AB                  | $\overline{C}\overline{D}$ | <i>CD</i> 01 | CD<br>11 | <i>CD</i> 10 |

|---------------------------|----------------------------|--------------|----------|--------------|

| $\frac{00}{A}\frac{B}{B}$ | 1                          | 1            | 0        | 1            |

| 11 2                      | 0                          | 1            | 3        | 2            |

| 01                        | 0                          | 1            | 1        | 0            |

| AB                        | 4                          | 5            | 7        | 6            |

| 11                        | 1                          |              | 1        | 1            |

| AB                        | 12                         | 13           | 15       | 14           |

| 10_                       |                            | 1            | 0        | 0            |

| AB                        | 0 8                        | 9            | 11       | 10           |

## Representing Standard SOP on K-Map

• Plot the Boolean expression  $Y = \overline{ABC} + \overline{ABC} + \overline{ABC}$  on the Karnaugh map.

BC 00 01 11 10 BC BC BC

Plot the Boolean expression  $Y = AB\overline{C}D + ABCD + \overline{ABCD} + \overline{ABCD} + \overline{ABCD}$  on the Karnaugh map.

• Represent the following in Karnaugh map  $f(a,b,c)=\Sigma m(1,4,6,7)$

| bc<br>a          | $\frac{00}{b}  \overline{c}$ | $\frac{01}{\overline{b}}$ c | 11<br>bc   | $\frac{10}{b\overline{c}}$ |

|------------------|------------------------------|-----------------------------|------------|----------------------------|

| $0 \overline{a}$ | 0 0                          | 1 1                         | 0 3        | 0 2                        |

| 1 a              | 1 4                          | 0 5                         | <b>1</b> 7 | <b>1</b> 6                 |

• Represent the following in Karnaugh map  $f(w,x,y,z)=\Sigma m(1,2,5,6,7,11,14)$

| X                                      | $\overline{y}\overline{z}$ 00 | $\overline{y}z$ 01 | yz<br>11 | у <u></u> 7 |

|----------------------------------------|-------------------------------|--------------------|----------|-------------|

| $\frac{00}{\overline{w}} \overline{x}$ | 0                             | 1                  | 3        | 2           |

| $\frac{\partial 1}{\overline{w}} x$    | 4                             | 5                  | 7        | 6           |

| 11<br>wx                               | 12                            | 13                 | 15       | 14          |

| $\frac{10}{w\overline{x}}$             |                               |                    |          |             |

|                                        | 8                             | 9                  | 11       | 10          |

#### **Representing Standard POS on K-Map:**

• Plot the Boolean expression Y = (A+B+C).  $(A+\overline{B}+C)$ .  $(A+B+\overline{C})$ .  $(A+B+\overline{C})$

| B+C<br>A         | 00<br>B + C | $01 \\ \text{B+}\overline{C}$ | $\frac{11}{B} + \overline{C}$ | $\frac{10}{B}$ +C |

|------------------|-------------|-------------------------------|-------------------------------|-------------------|

| 0 A              | 0 0         | 0 <sub>1</sub>                | <b>0</b> 3                    | <mark>0</mark> 2  |

| 1 $\overline{A}$ | 1 4         | 1 5                           | 1 7                           | 1 6               |

• Plot the expression F(A,B,C,D) = (A+B+C+D).  $(A+\overline{B}+C+D)$ .  $(A+B+\overline{C}+D)$ .

$(A+\overline{B}+\overline{C}+D)$ .  $(A+B+\overline{C}+\overline{D})$

| C+D<br>A+B                               | C+D<br>00 | $C + \overline{D}$ 01 | $\overline{C} + \overline{D}$ 11 | <u>C</u> +D<br>10 |

|------------------------------------------|-----------|-----------------------|----------------------------------|-------------------|

| $00 \\ A + B$                            | 0         | 1                     | 3                                | 2                 |

| $\frac{01}{A+\overline{B}}$              | 4         | 5                     | 7                                | 6                 |

| $\frac{11}{\overline{A} + \overline{B}}$ |           |                       |                                  |                   |

|                                          | 12        | 13                    | 15                               | 14                |

| <i>10</i><br><del>Ā</del> +B             | 0         | 0                     | 11                               | 10                |

• Represent the function in k-map  $f=\pi M(1,4,6,9,11)$

| C+D<br>A+B                    | C+D<br>00 | $C + \overline{D}$<br>01 | $\overline{C} + \overline{D}$ 11 | <u>C</u> +D 10 |

|-------------------------------|-----------|--------------------------|----------------------------------|----------------|

| 00                            | 1         |                          | 1                                | 1              |

| A + B                         | 0         | 0 1                      | 3                                | 2              |

| <u>01</u>                     |           | 1                        | 1                                | 0              |

| $A+\overline{B}$              | 0 4       | 5                        | 7                                | 6              |

| 11                            |           |                          |                                  |                |

| $\overline{A} + \overline{B}$ |           | 1                        | _                                | 1              |

|                               | 1         |                          | 1                                |                |

|                               | 12        | 13                       | 15                               | 14             |

| 10                            |           |                          |                                  |                |

| $\overline{A}$ +B             |           |                          |                                  | 1              |

|                               | 1         |                          | 0                                |                |

|                               | 8         | 0 9                      | 11                               | 10             |

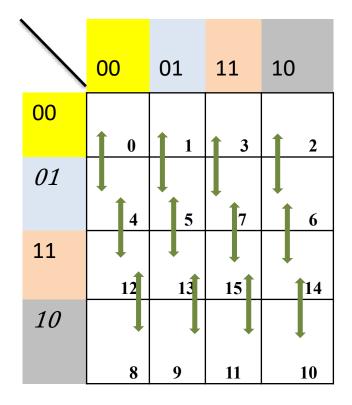

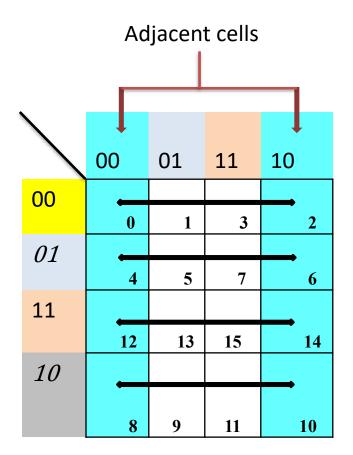

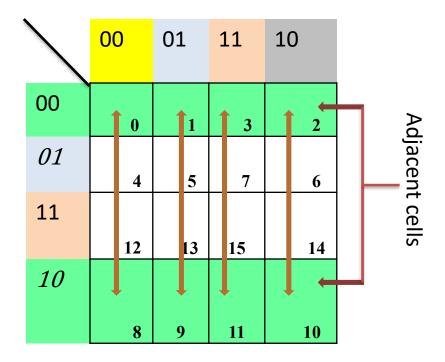

## Grouping cells for simplification

- Once the Boolean function is plotted on the Karnaugh map we have to use grouping technique to simplify the Boolean function.

- The grouping is nothing combining terms in adjacent cells.

- Two cells are said to be adjacent if they conform the single change rule.,i.e., there is only one variable difference between co-ordinates of two cells.

## **Grouping Two Adjacent Ones(Pair)**

Neighbouring cells in the row are adjacent

Neighbouring cells in the column are adjacent

Leftmost and corresponding rightmost cells are adjacent

Top and corresponding bottom cells are adjacent

# $Y = \bar{A}BC + ABC$

| A BC             |   | $\frac{01}{B}$ C | 11<br>BC              | 10<br>В <u>С</u> |

|------------------|---|------------------|-----------------------|------------------|

| $0 \overline{A}$ | 0 | 1                | 1 3                   | 2                |

| 1 A              | 4 | 5                | <b>1</b> <sub>7</sub> | 6                |

$$Y = \bar{A}\bar{B}C + \bar{A}BC + ABC$$

$$Y = \bar{A}C + BC$$

| CD<br>AB                                                   | $\overline{C}\overline{D}$ | <i>C D</i> 01 | CD<br>11 | <i>CD</i> 10 |

|------------------------------------------------------------|----------------------------|---------------|----------|--------------|

| $\frac{00}{\overline{A}}\frac{\overline{B}}{\overline{B}}$ | 0                          | 1 1           | 3        | 2            |

| $\frac{O1}{\overline{A} B}$                                | 4                          | 5             | 7        | 6            |

| 11<br>AB                                                   | 12                         | 13            | 15       | 14           |

| $\frac{10}{A  \overline{B}}$                               | 8                          | 1             | 11       | 10           |

$$Y = \bar{B}\bar{C}D$$

## Grouping four adjacent ones(Quad)

|                             |                             |                  |     |                 |            | <b>C</b> D                  | $\overline{C} \overline{D}$ | $\overline{C}D$ | CD | $C\overline{D}$ |

|-----------------------------|-----------------------------|------------------|-----|-----------------|------------|-----------------------------|-----------------------------|-----------------|----|-----------------|

| BC                          | 00                          | 01               | 11  | 10              |            | AB                          | 00                          | 01              | 11 | 10              |

| A \                         | $\overline{B} \overline{C}$ | $\overline{B}$ C | ВС  | B <del>C</del>  |            | 00                          | 0                           | 1               | 0  | 0               |

| o $\overline{A}$            | 0 0                         | 0 1              | 0 3 | 0 2             |            | $\overline{A} \overline{B}$ | 0                           | 1               | 3  | 2               |

| 1 A                         | 1 4                         | 1 5              | 1 7 | 16              | <b>→</b> A | 01                          | 0                           | 1               | 0  | 0               |

|                             |                             |                  |     |                 |            | $\overline{A} B$            | 4                           | 5               | 7  | 6               |

| CD                          | $\overline{C}\overline{D}$  | $\overline{C}D$  | CD  | $C\overline{D}$ |            | 11                          | 0                           | 1               | 0  | 0               |

| AB                          | 00                          | 01               | 11  | 10              | 4          | AB                          | 12                          | 13              | 15 | 14              |

| 00                          | 0                           | 0                | 0   | 0               |            | 10                          |                             | 1               | 0  | 0               |

| $\overline{A} \overline{B}$ | 0                           | 1                | 3   | 2               |            | $A \overline{B}$            | 0 8                         | 9               | 11 | 10              |

| $\frac{01}{1}$              | 0                           | 1                | 1   | 0               |            |                             |                             |                 |    |                 |

| $\overline{A} B$            | 4                           | 5                | 7   | 6               |            |                             |                             |                 |    |                 |

| 11                          | 0                           | 1                | 1   | 0               |            |                             |                             | $\overline{C}D$ |    |                 |

| AB                          | 12                          | 13               | 15  | 14              |            |                             |                             |                 |    |                 |

| 10_                         |                             | 0                | 0   | 0               |            |                             |                             |                 |    |                 |

| $A \overline{B}$            | 0 8                         | 9                | 11  | 10              | BD         | )                           |                             |                 |    |                 |

| CD<br>AB                    | $\overline{C}\overline{D}$ | <i>C</i> D 01 | CD<br>11 | <i>CD</i> 10 |

|-----------------------------|----------------------------|---------------|----------|--------------|

| 00                          | 1                          | 0             | 0        | 1            |

| $\overline{A} \overline{B}$ | 0                          | 1             | 3        | 2            |

| 01                          | 0                          | 0             | 0        | 0            |

| $\overline{A} B$            | 4                          | 5             | 7        | 6            |

| 11                          | 0                          | 0             | 0        | 0            |

| AB                          | 12                         | 13            | 15       | 14           |

| 10                          | 1                          | 0             | 0        | 1            |

| $A \overline{B}$            | 8                          | 9             | 11       | 10           |

|                             |                            |               |          |              |

| CD<br>AB                    | $\overline{C}\overline{D}$ | <i>CD</i> 01 | CD<br>11 | <i>CD</i> 10 |

|-----------------------------|----------------------------|--------------|----------|--------------|

| 00                          | 0                          | 0            | 0        | 0            |

| $\overline{A} \overline{B}$ | 0                          | 1            | 3        | 2            |

| 01                          | 0                          | 0            | 0        | 0            |

| $\overline{A} B$            | 4                          | 5            | 7        | 6            |

| 11                          | 1                          | 0            | 0        | 1            |

| AB                          | 12                         | 13           | 15       | 14           |

| 10                          | 1                          | 0            | 0        | 1            |

| $A\overline{B}$             | 8                          | 9            | 11       | 10           |

$A\overline{D}$

$\overline{B}\overline{D}$

# **Grouping Eight Adjacent Ones (Octet)**

| CD<br>AB                                                   | $\overline{C}\overline{D}$ 00 | <i>C D</i> 01 | CD<br>11 | <i>CD</i> 10 |

|------------------------------------------------------------|-------------------------------|---------------|----------|--------------|

| $\frac{00}{\overline{A}}\frac{\overline{B}}{\overline{B}}$ | 0                             | 1             | 1 3      | 0            |

| $\frac{O1}{\overline{A}B}$                                 | 0                             | 1 5           | 1 7      | 0            |

| 11<br>AB                                                   | 0                             | 1 13          | <i>1</i> | <i>O</i>     |

| $\frac{10}{A \overline{B}}$                                | 0 8                           | 9             | 1        | 0            |

| CD<br>AB                    | <i>C D</i> 00 | <i>CD</i> 01 | CD<br>11 | <i>CD</i> 10 |   |   |

|-----------------------------|---------------|--------------|----------|--------------|---|---|

| 00                          | 0             | 0            | 0        | 0            |   |   |

| $\overline{A} \overline{B}$ | 0             | 1            | 3        | 2            |   |   |

| 01                          | 1             | 1            | 1        | 1            |   |   |

| $\overline{A} B$            | 4             | 5            | 7        | 6            |   |   |

| 11                          | 1             | 1            | 1        | 1            | E | 3 |

| AB                          | 12            | 13           | 15       | 14           |   |   |

| 10                          |               | 0            | 0        | 0            |   |   |

| $A \overline{B}$            | 0 8           | 9            | 11       | 10           |   |   |

| AB AB            | <u>C</u> <u>D</u><br>00 | <i>CD</i> 01 | CD<br>11 | <i>CD</i> 10 |

|------------------|-------------------------|--------------|----------|--------------|

| 00               | 1                       | 1            | 1        | 1            |

| AB               | 0                       | 1            | 3        | 2            |

| 01               | 0                       | 0            | 0        | 0            |

| $\overline{A} B$ | 4                       | 5            | 7        | 6            |

| 11               | 0                       | 0            | 0        | 0            |

| AB               | 12                      | 13           | 15       | 14           |

| 10               | 1                       | 1            | 1        | 1            |

| $A \overline{B}$ | 8                       | 9            | 11       | 10           |

| CD<br>AB                    | <i>C D</i> 00 | <i>CD</i><br>01 | CD<br>11 | <i>CD</i> 10 |  |

|-----------------------------|---------------|-----------------|----------|--------------|--|

| 00                          | 1             | 0               | 0        | 1            |  |

| $\overline{A} \overline{B}$ | 0             | 1               | 3        | 2            |  |

| 01                          | 1             | 0               | 0        | 1            |  |

| $\overline{A} B$            | 4             | 5               | 7        | 6            |  |

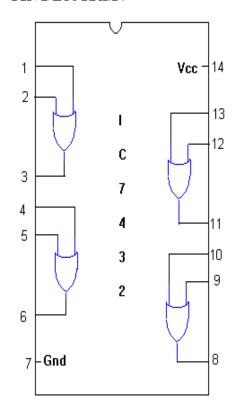

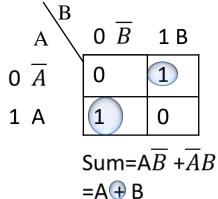

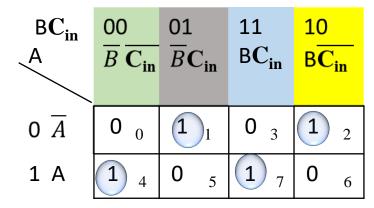

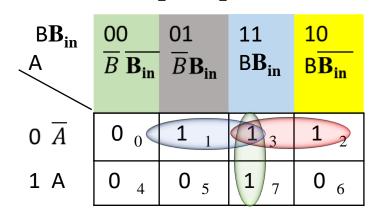

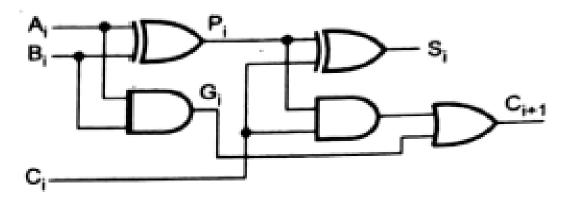

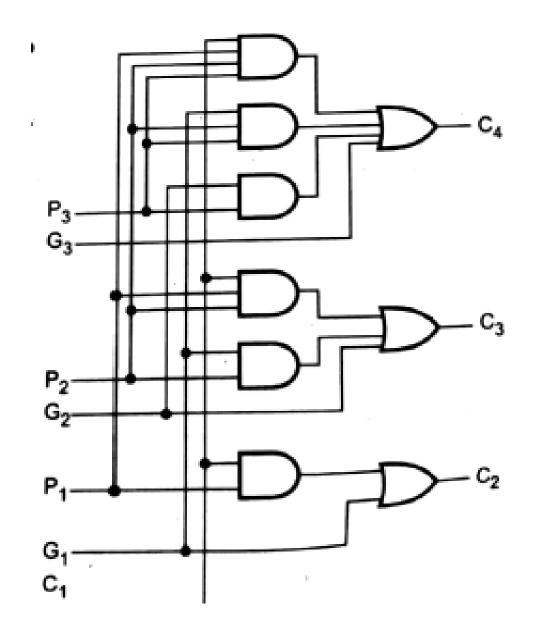

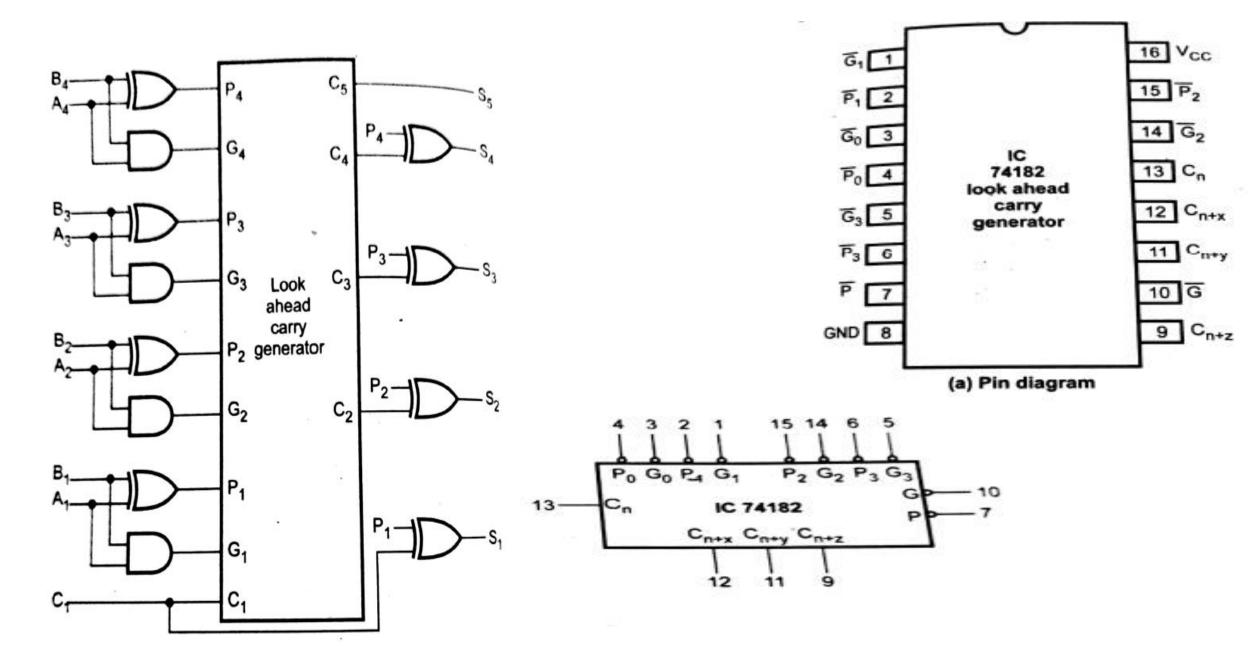

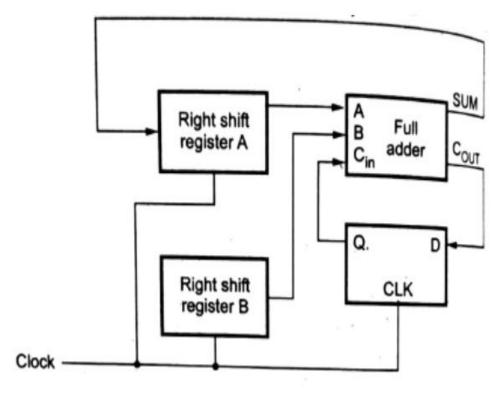

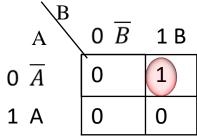

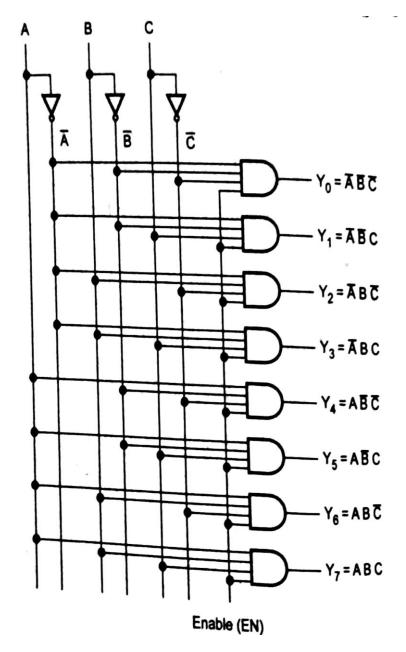

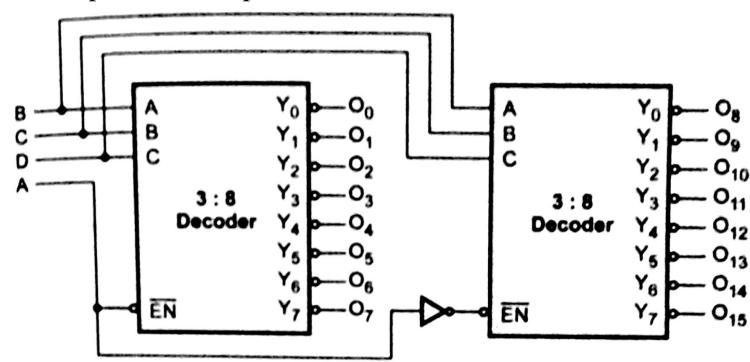

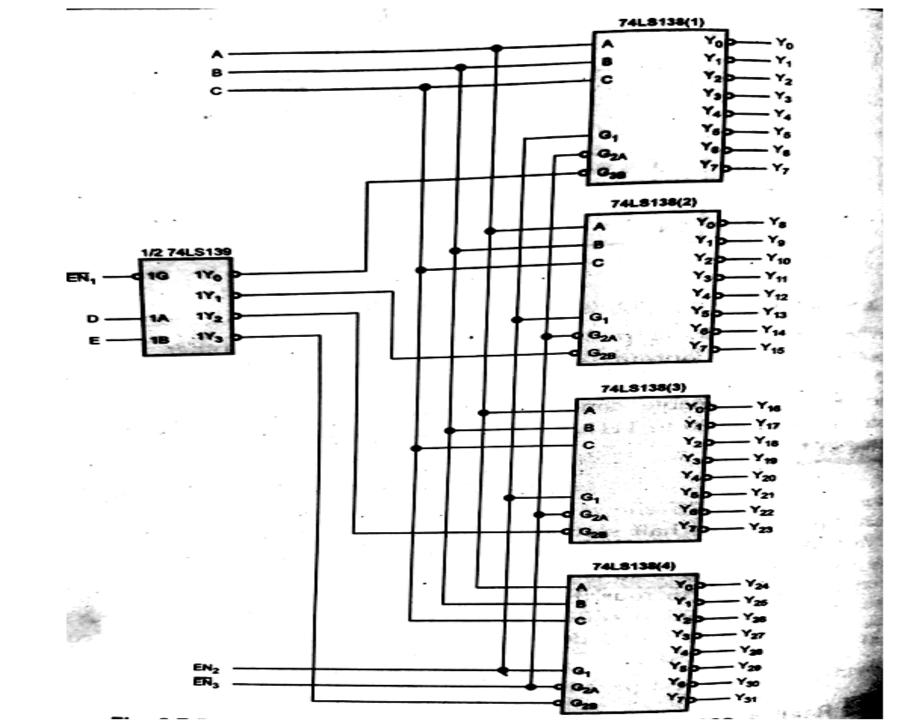

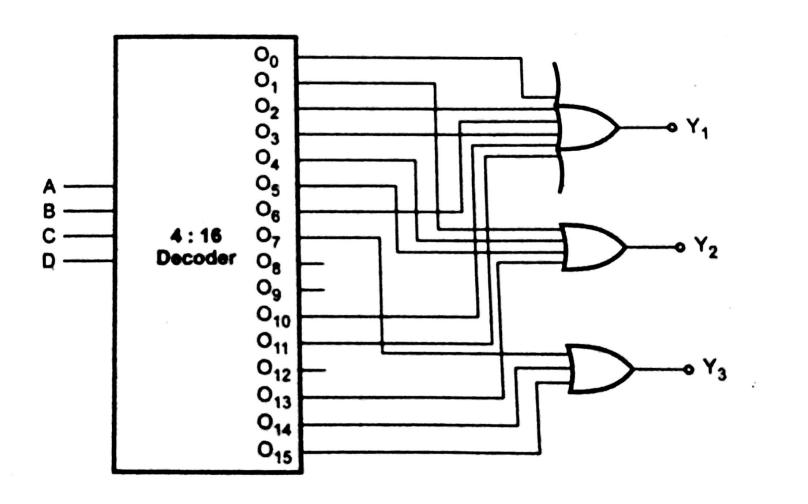

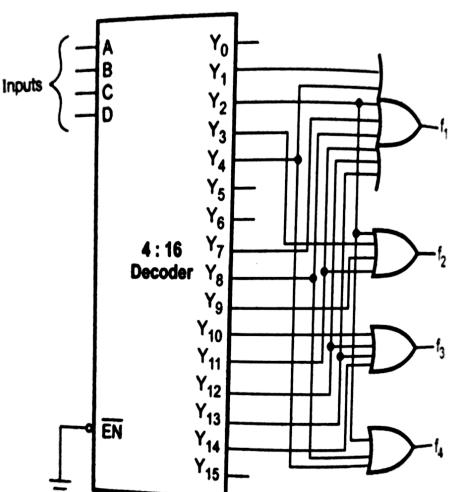

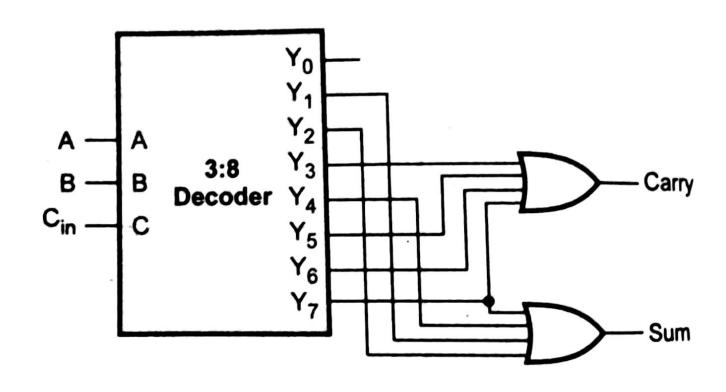

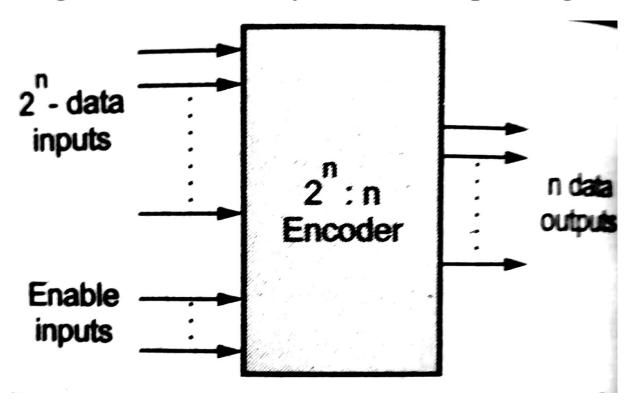

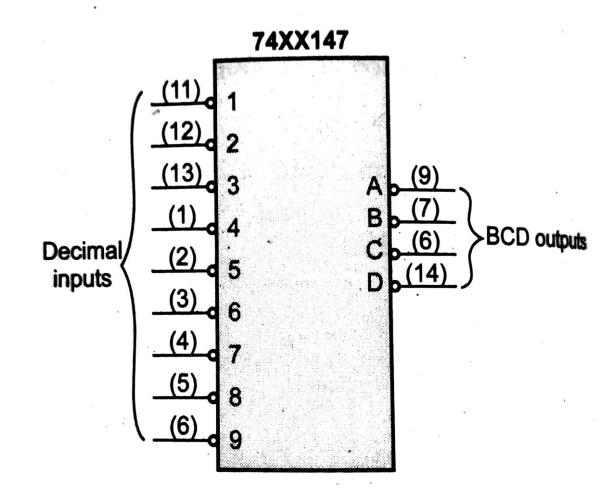

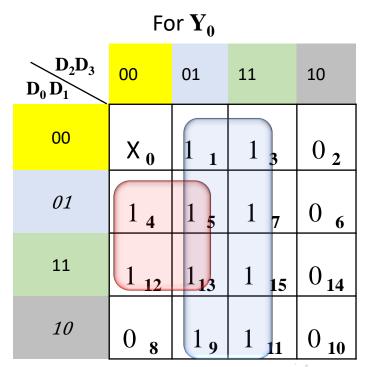

| 11                          | 1             | 0               | 0        | 1            |  |